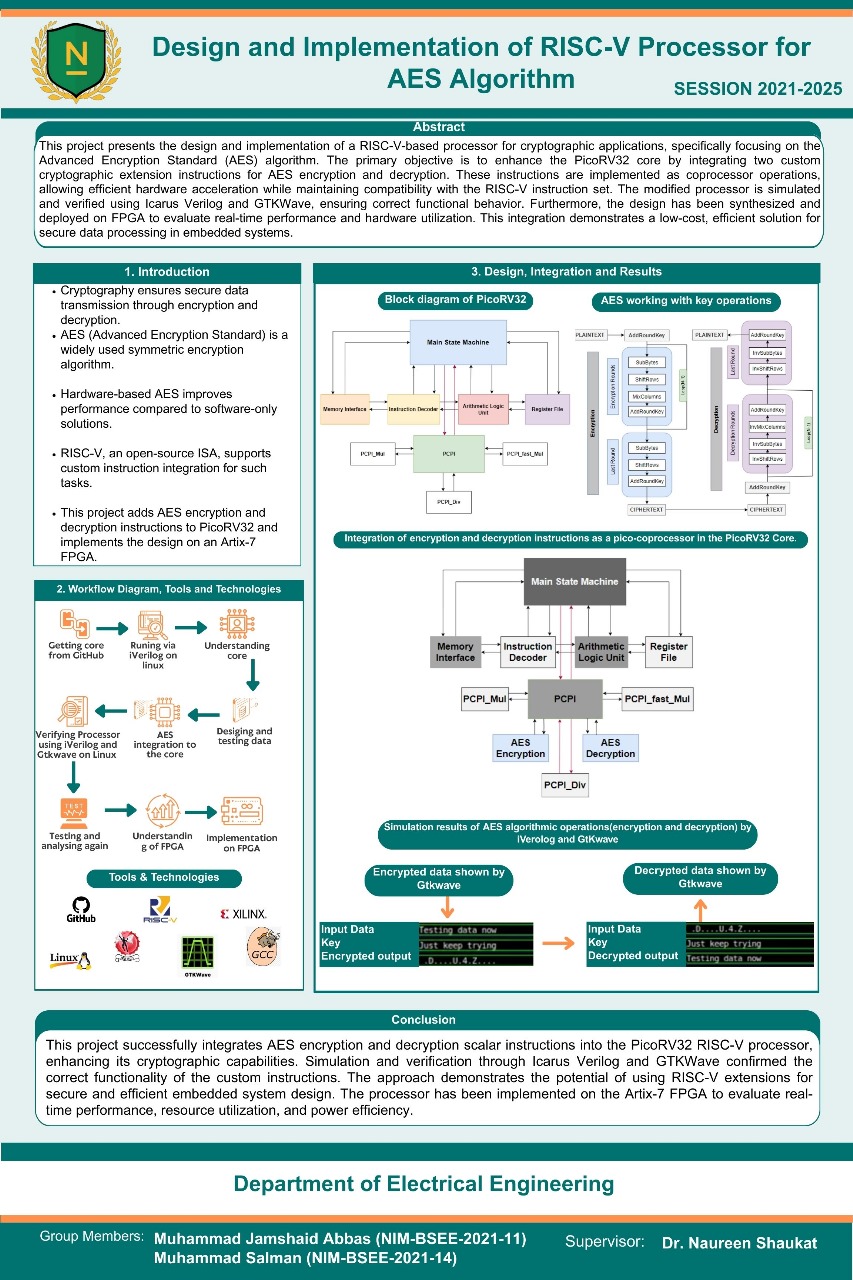

This project integrates two AES instructions (encryption and decryption) as a coprocessor into the PicoRV32 RISC-V core. By implementing these hardware- accelerated instructions, cryptographic performance is significantly improved while maintaining full RISC-V compatibility. The design was functionally verified using Icarus Verilog and GTKWave, followed by FPGA implementation to assess real- time performance and resource efficiency. The result is a low-cost, high-efficiency solution for secure embedded systems.

Keywords: RISC-V,Cyptography,AES,PICORV32,FPGA

Tools: GCC COMPILER,GCC,IVERILOG,GTKWAVE,DESIGN ISE TOOL

Department: Department of Electrical Engineering

Tools: GCC COMPILER,GCC,IVERILOG,GTKWAVE,DESIGN ISE TOOL

Department: Department of Electrical Engineering

Project Poster