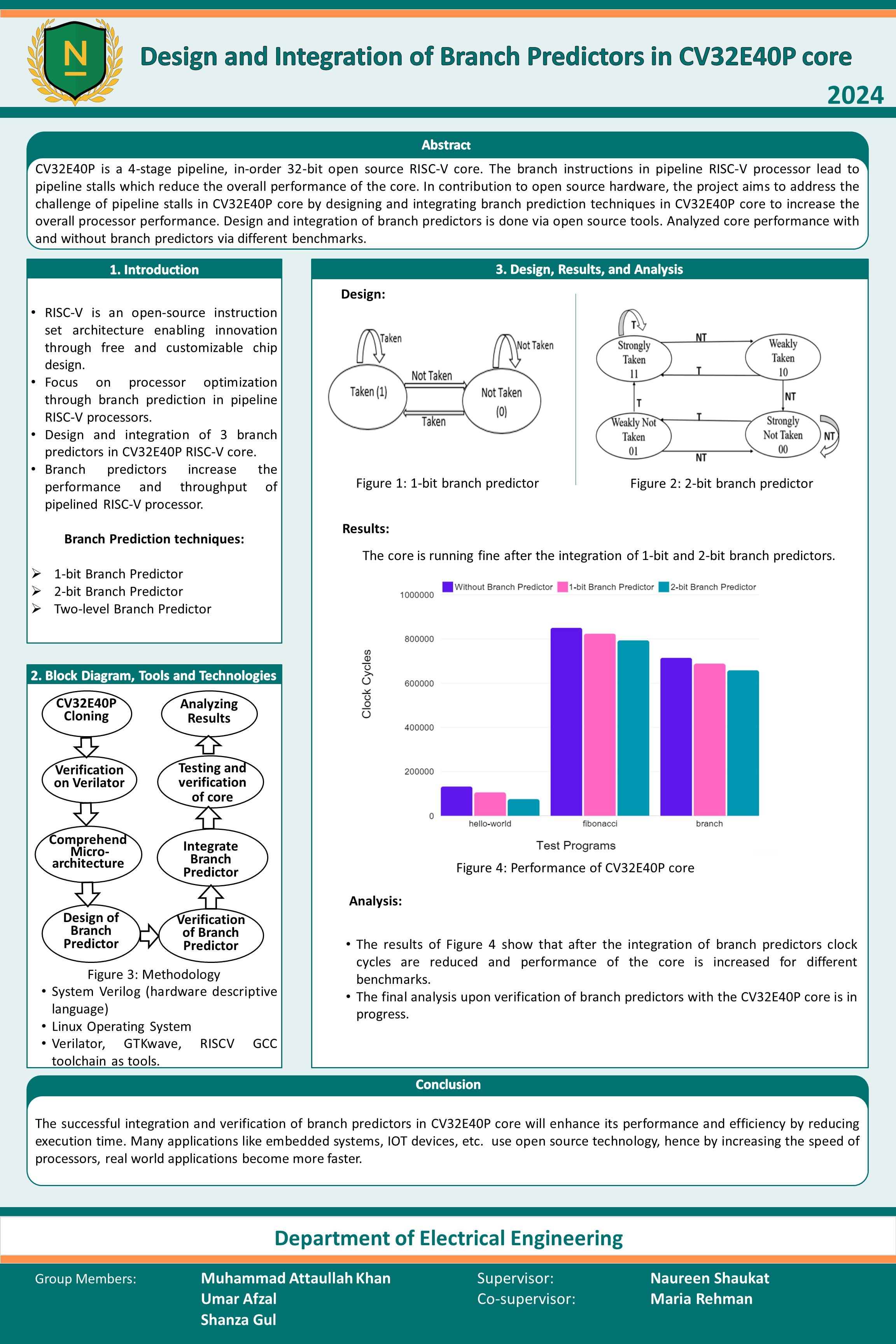

The project deals with the control hazards in CV32E40P core of pipelined RISC-V processor. On branch taken decision in conditional instructions, the execution flow changes from sequential to non-sequential causing control hazard in pipelined architecture. It results in the increment of clock cycles per instruction and due to which the execution time increases for the instruction and performance of the processor decreases. We designed branch predictors to improve the efficiency and throughput of a pipeline RISC-V processor. Our project focuses on the design of three branch prediction techniques 1-bit, 2-bit and correlation branch predictors that predict the outcomes of instructions in fetch stage using different methodologies. Through the literature review, it is determined that the branch predictor is not available currently in CV32E40p core. This project involves understanding of the micro-architecture of pipeline core CV32E40p on which the predictor is to be integrated, implementation of various techniques related to branch prediction, and their integration in current architecture. It leads us to develop our corresponding algorithm which is embedded in the fetch and decode stages and several test programs are run to verify the proper working of integrated algorithm. The analysis show that after the integration of different branch predictors clock cycles reduced and performance of the core increased for different benchmarks.

Tools: RISC-V GCC Toolchain,System Verilog,Verilator,GTKwave,Linux,Iverilog,EDA Playground,Modelsim

Department: Department of Electrical Engineering

Project Poster