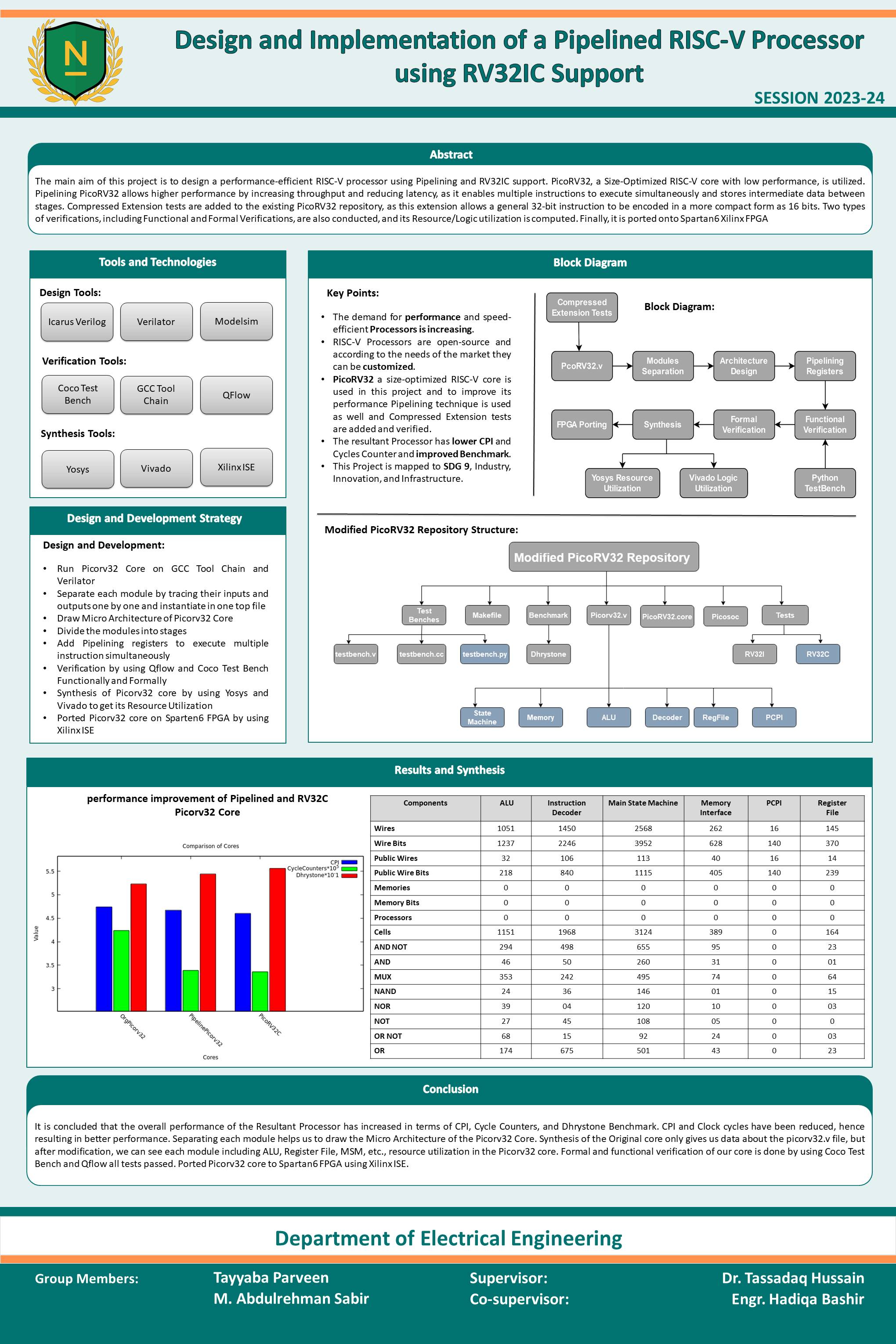

Design and Implementation of a Pipelined RISC-V Processor with RV32IC Support

Processors are the brains of the computers. They execute instructions and perform calculations. Due to their customize-able and open-source nature, RISC-V Processors usage is increasing day-by-day. But at the same time, the speed and performance of these processors also matter a lot. We are working with a RISC-V core PicoRV32 that is size-optimized with low performance. Using Pipelining we are trying to increase its performance of PiocRV32 core by executing multiple instructions simultaneously. As a result, the CPI (cycles per instruction) is reduced and its throughput is improved. The Benchmark used in our project is Dhrystone DMIPS/MHz. The result will also be functionally and formally by verified and after computing its resource and logic utilization, it will be ported on FPGA.

Keywords: pipelining,processors,PicoRV32,RISC-V ,Verification

Tools: GCC Toolchain,Vivado,Yosys,Verilator,Icarus verilog,Xilinx ISE,Open Lane,GTKWAVE

Department: Department of Electrical Engineering

Project Team Members

| Name |

Email |

|

Muhammad Abdulrehman Sabir

|

abdul2020@namal.edu.pk |

|

Tayyaba Parveen

|

tayyaba2020@namal.edu.pk |

Project Poster