Integration of Bit Manipulation Extension in the SweRV EH1 Core of RISC-V Processor and its Verification Using Standard Tools

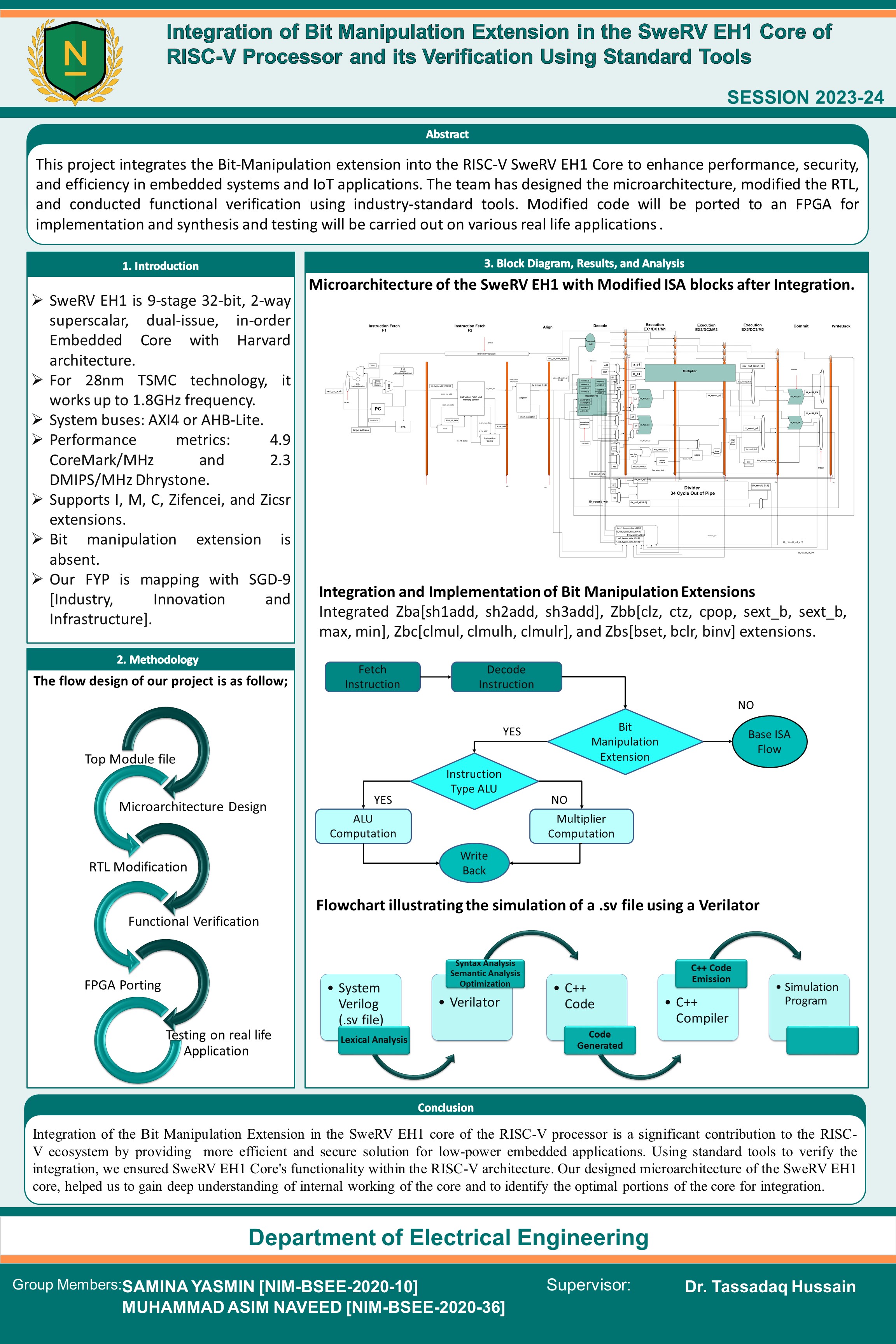

This project integrates the Bit-Manipulation extension into the RISC-V SweRV EH1 Core to enhance performance, security, and efficiency in embedded systems and IoT applications. The team has designed the microarchitecture, modified the RTL, and conducted functional verification using industry-standard tools. Modified code will be ported to an FPGA for implementation and synthesis and testing will be carried out on various real life applications .

Keywords: RISC-V, SweRV EH1 Core, Micro-architecture, Bit Manipulation, Embedded Applications, Performance, Efficiency, Security

Tools: Tools: Verilator, GCC Toolchain, Xilinx Tools like Vivado,Technologies: System Verilog, Verilog, C/C++,Techniques: Functional Verification, Performance Analysis

Department: Department of Electrical Engineering

Project Team Members

| Name |

Email |

|

Samina Yasmin

|

saminayasmin2020@namal.edu.pk |

|

Muhammad Asim Naveed

|

asim2020@namal.edu.pk |

Project Poster